## Contexte : attestation à distance

### Objectif

Vérifier l'intégrité d'un algorithme et de son environnement d'exécution sur une machine distante.

### Modèle de menace fort

L'adversaire peut intégralement corrompre le code et les données de l'algorithme ainsi que son environnement d'exécution.

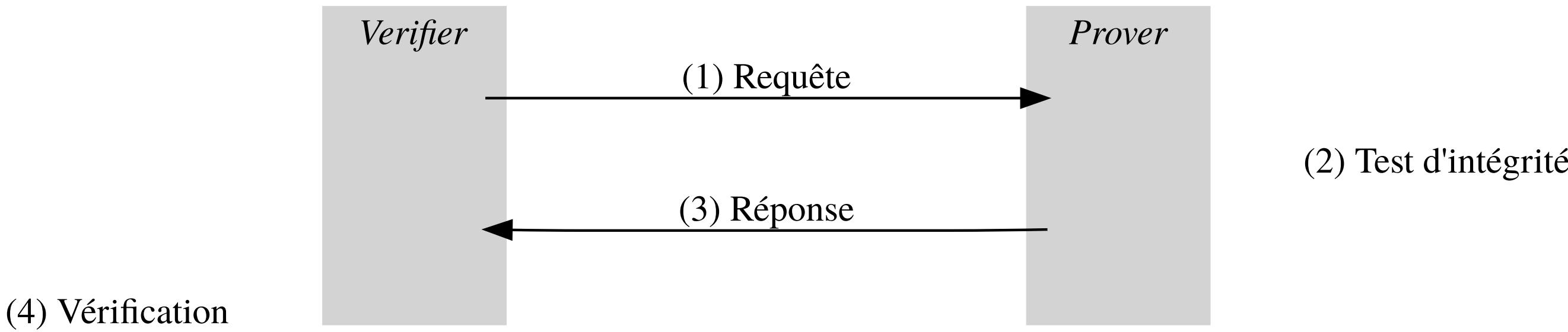

- $\mathcal{V}_{rf}$  envoie une requête ainsi qu'un challenge à  $\mathcal{P}_{rv}$ .

- $\mathcal{P}_{rv}$  calcule un test d'intégrité authentifié  $\Sigma$  sur son environnement et le challenge.

- $\mathcal{P}_{rv}$  renvoie  $\Sigma$  à  $\mathcal{V}_{rf}$

- $\mathcal{V}_{rf}$  vérifie  $\Sigma$  et décide s'il correspond à un état de  $\mathcal{P}_{rv}$  valide

### Intégrité de $\Sigma$

Calcul de  $f_k : c, m \mapsto \text{HMAC}(m||c, k) = \Sigma$ .

- $c$  : challenge, permet d'emêcher le re-jeu d'une réponse

- $m$  : mémoire et environnement à attester

- $k$  : secret partagé

Protection du secret : support matériel pour les contrôles d'accès

## Vérification formelle (extrait de VRASED : A Verified Hardware-Software Co-Design for Remote Attestation)

Intégrité de  $\Sigma$ , élimination de vulnérabilités :

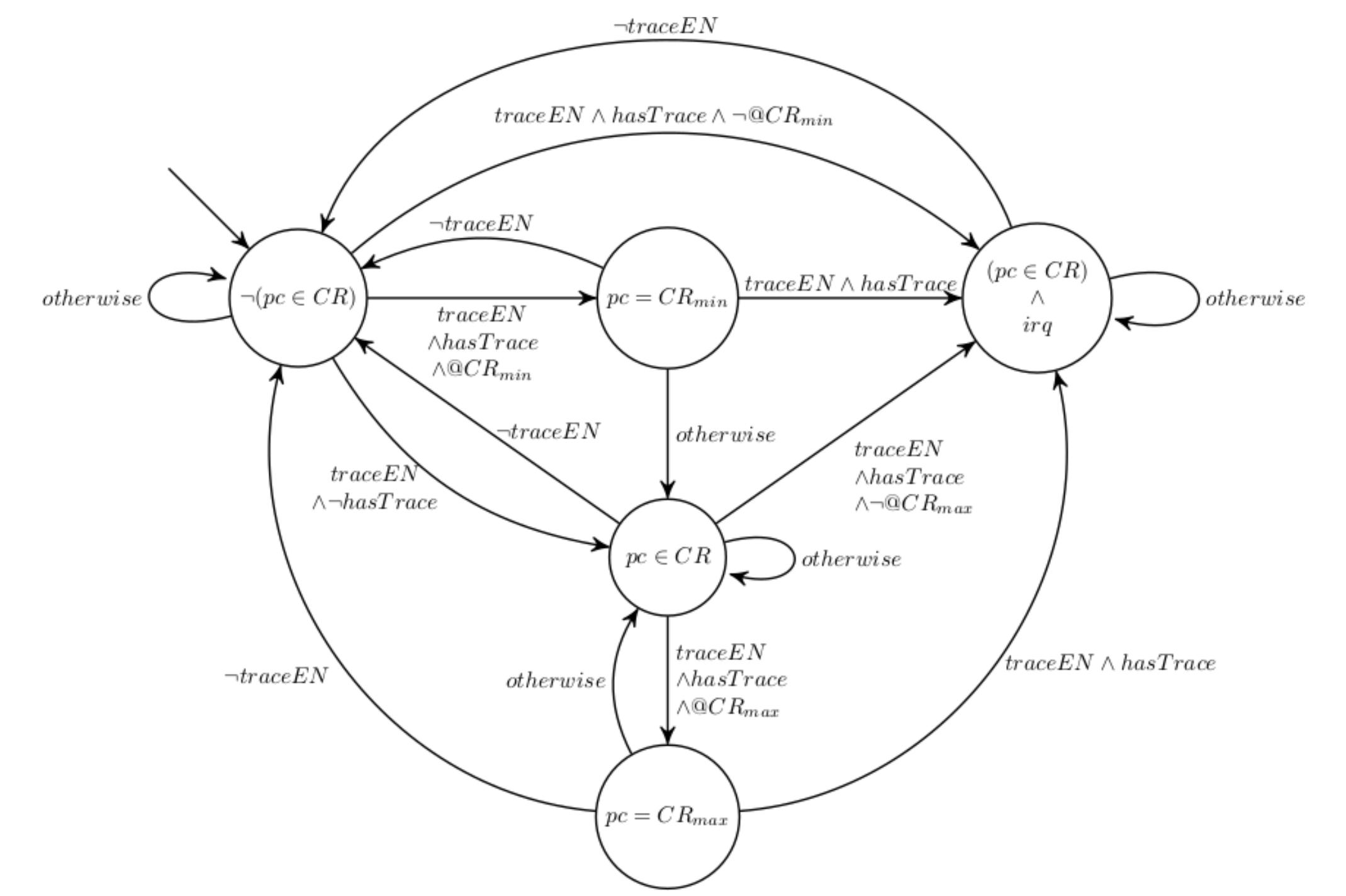

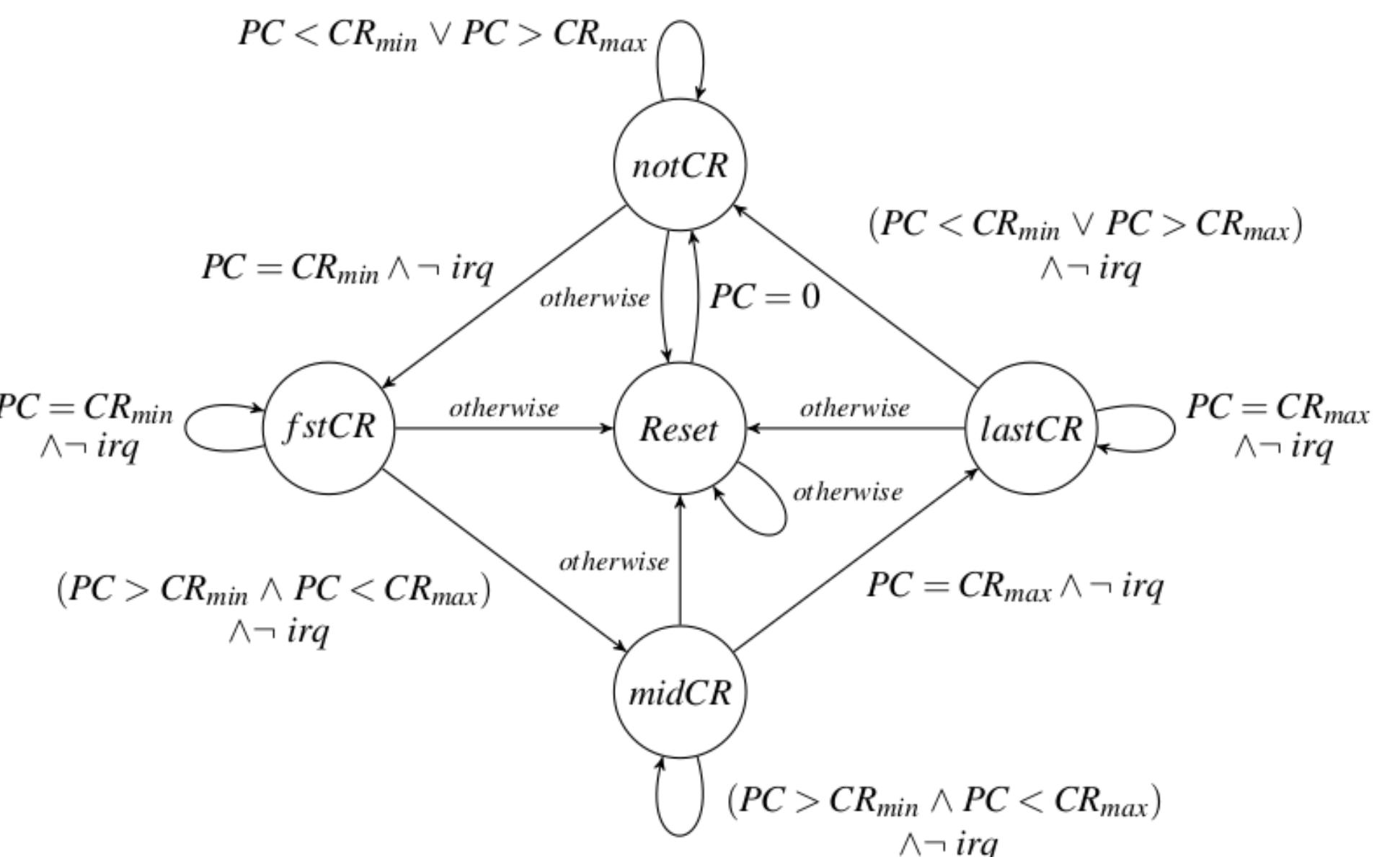

- modélisation du système (automate)

- spécification formelle (invariants, propriétés temporelles)

- model-checking : vérification des propriétés

- preuve de sécurité : absence de vulnérabilité

$$G\{\neg\text{reset} \wedge \neg(PC \in CR) \wedge X(PC \in CR) \rightarrow PC = CR_{min} \vee X(\text{reset})\} \quad (1)$$

$$G\{\neg\text{reset} \wedge (PC \in CR) \wedge \neg X(PC \in CR) \rightarrow PC = CR_{max} \vee X(\text{reset})\} \quad (2)$$

$$G\{irq \wedge (PC \in CR) \rightarrow \text{reset}\} \quad (3)$$

$$G\{\neg(PC \in CR) \wedge R_{en} \wedge (D_{addr} \in KR) \rightarrow \text{reset}\} \quad (4)$$

Preuve de sécurité :

$$LTL_1 \wedge LTL_2 \wedge LTL_3 \wedge LTL_4 \rightarrow \text{Theorem}$$

## Problématique

Pas de modification lourde du cœur :

- accès aux bus d'adresse ( $D_{addr}$ )

- accès au compteur ordinal ( $PC$ )

## Solution proposée

Architecture :

- processeur pris sur étagère + FPGA (Zynq 7000)

- profiter des preuves de sécurité de VRASED, attestation à distance sur microcontrôleur

Transducteur vers alphabet d'entrée du moniteur :

- esclave AXI pour socket  $k$  et  $f$  ( $D_{addr}$ )

- décodeur de traces CoreSight + instructions spécifiques ( $PC$ )